From our front-page news:

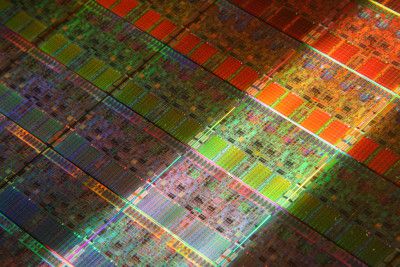

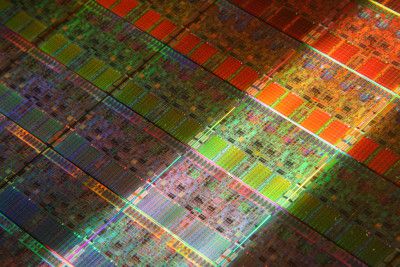

The term '3D Chip' might sound a bit misleading, and it might very-well be. When I first heard the term, I thought it was another GPU processor, but '3D' is meant to be taken literally. All current processors out there now are 2D... flat, with components found to the right and left of each other. Researchers at the University of Rochester have developed what they claim to be the first true 3D processor, running at 1.4GHz.

A true 3D processor is one that has stacked components, rather than the side-by-side components found on all current chips. The benefits would be better efficiency, better performance and a far better footprint. One researcher noted that while we will hit a barrier with horizontal chips, vertical chips will scale indefinitely. I can see it now... installing a pole rather than a flat piece of silicon.

Of course things shouldn't get that bad, but the prospect of a 3D chip is an interesting one. What would concern me is the cooling-ability. How is it that a cube chip could be effectively cooled? With '2D' chips, they lay flat, and obviously that works out to our favor with cooling. A cube chip wouldn't be able to use a standard CPU cooler design, but rather something entirely different. Regardless, there are obvious hurdles, but it's an interesting prospect nonetheless.

The hardest part according to the researchers is getting the levels of the chip to properly interact. Professor Friedman compares the problem to a scenario where a standard microprocessor is like the U.S. traffic system, and then the 3D processor is like 3 or more U.S. traffic systems stacked atop each other and expected to coordinate traffic between levels. He says the problem is even tougher as the processors are different, so it’s more like stacking the U.S., China, and India, where traffic laws are different, atop each other.

Source: University of Rochester Press Release , Via: DailyTech

A true 3D processor is one that has stacked components, rather than the side-by-side components found on all current chips. The benefits would be better efficiency, better performance and a far better footprint. One researcher noted that while we will hit a barrier with horizontal chips, vertical chips will scale indefinitely. I can see it now... installing a pole rather than a flat piece of silicon.

Of course things shouldn't get that bad, but the prospect of a 3D chip is an interesting one. What would concern me is the cooling-ability. How is it that a cube chip could be effectively cooled? With '2D' chips, they lay flat, and obviously that works out to our favor with cooling. A cube chip wouldn't be able to use a standard CPU cooler design, but rather something entirely different. Regardless, there are obvious hurdles, but it's an interesting prospect nonetheless.

The hardest part according to the researchers is getting the levels of the chip to properly interact. Professor Friedman compares the problem to a scenario where a standard microprocessor is like the U.S. traffic system, and then the 3D processor is like 3 or more U.S. traffic systems stacked atop each other and expected to coordinate traffic between levels. He says the problem is even tougher as the processors are different, so it’s more like stacking the U.S., China, and India, where traffic laws are different, atop each other.

Source: University of Rochester Press Release , Via: DailyTech